What are Digital Latches? | SR-Latches | D-Latches

Hi mentees, we are here with a new tutorial. I hope you all are fine. So far, we have been designing combinational circuits i.e. Adder, Subtractor, Multiplexer etc. using logic gates. But from today onward, we will design sequential circuits using logic gates i.e. Latches, Flip Flops etc. Let's quickly recall what's the difference between combinational & Sequential Circuits:

Combinational Circuits:

- Combinational circuits only use the current state of the input values to generate the output.

- Examples of DLD Combinational Circuits are: Adders, Subtractors, Multiplexers etc.

Sequential Circuits

- Sequential Circuits use both the current & previous states of the inputs to generate the output.

- Examples of DLD Sequential Circuits are: Latches, Flip Flops, Timers, Counters etc.

Digital Memory Elements

Normally two types of memory elements are used in digital circuits to store binary data, named:

- Latches

- Flip Flops(We will cover in the next lecture)

As today's lecture is on Latches, so let's explore it:

What are Latches?

- Latches are used in digital circuits as a memory element and are used to store/save the input states.

The two inputs of Latches are called "S" and "R" where S stands for SET and R stands for RESET. Due to inputs , latches can have four unique combinations of the input. The output is denoted as "Q" and is totally dependent on the input Combination.

Nevertheless, another Output is also used in the circuit sometimes. this output is denoted as Q' and is read as Q bar, Complement of Q or bar Q NOT Q because it is also written as:

One can have an idea that this output is the invert result of "Q" output and depends on the Q and successively to the inputs S and R.

Two types of circuits are possible in latches:

- Active high circuits.

- Active low circuits.

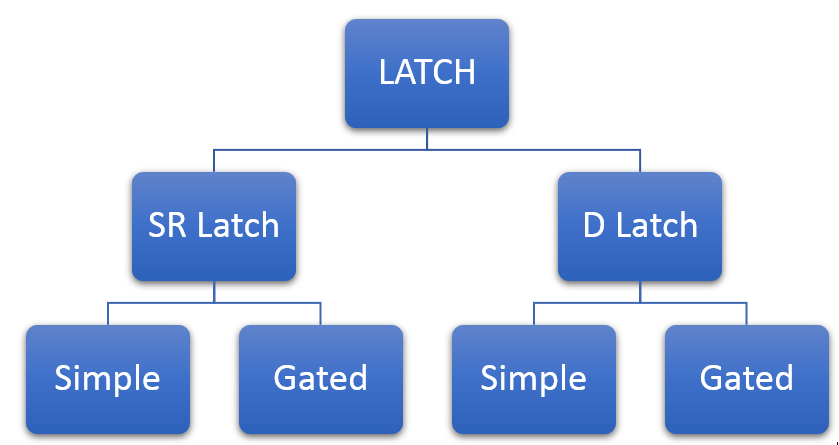

TYPES OF LATCHES

- SR Latches

- D Latches.

- Simple

- Gated

Prior to start DO YOU KNOW???????

- Logic Probes are used to give input to the circuit. They can only give two types of inputs:

- High ( Denoted by 1)

- Low ( Denoted by 0)

- By the same token, Logic toggle show the output. There are two types of output:

- High ( Denoted by 1)

- Low ( Denoted by 0)

- NAND gate shows the output LOW ( or 0) only when both the inputs are HIGH.

- NOT gate show is an inverter gate.

- NOR gate shows the output HIGH ( or 1) only when both the inputs are HIGH.

Implementation of Latches in Proteus ISIS

For best understanding, we'll design each of the type and create the truth table. Devices Required:- AND Gate

- NOT Gate

- Three input AND Gate

- Logic Toggle

- Logic Probe

- Clock

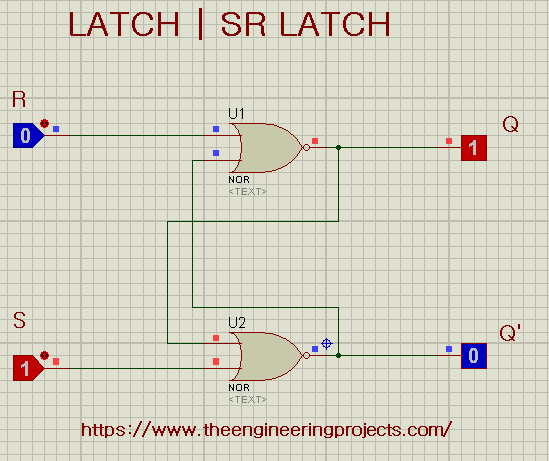

1. SR Latches in Proteus ISIS

- Choose Two NOR Gates and fix them on the working area.

- Examine the Circuit diagram and arrange the other required Components according to the Circuit diagram.

- Truss all the Components by wires with the help of circuit diagram.

- Pop the Play button and fill the truth table.

| S | R | Q | Q’ |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 |

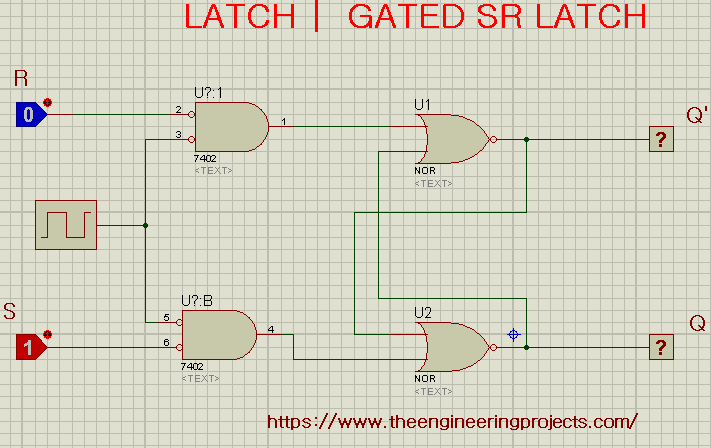

2. Gated SR Latch in Proteus ISIS

The SR latch are not Complete, hence the performance can be enhanced by the a process called "Gating" , and the resultant circuit is called Gated SR Circuit.

- We add two Positive NOR gates at the input "S" and "R" that have inverted input using NOT Gates. In this way we can examine the Condition more clearly when both the inputs in SR gate were HIGH.

- The circuit works well when we add a clock in the two inputs of the NOR gates.

| CLK | S | R | Q | Q’ |

| 0 | X | X | LATCH | LATCH |

| 1 | 0 | 0 | LATCH | LATCH |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 0 |

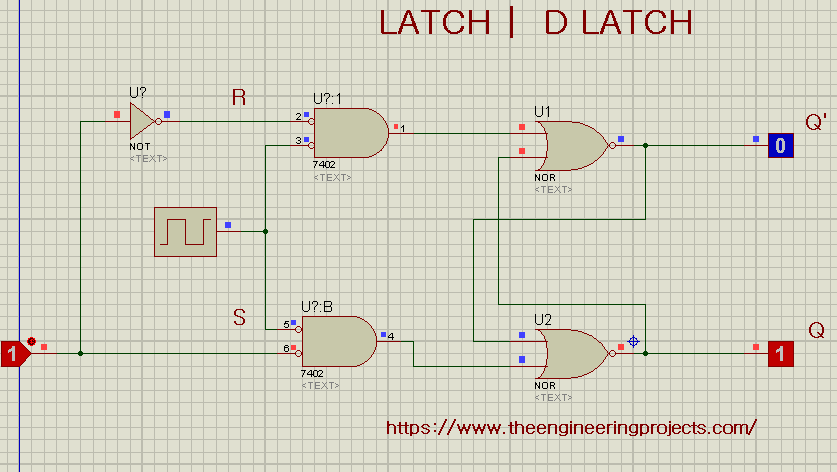

3. D Latches in Proteus ISIS

D latch is a modification of the Gated SK Latch.- we add the NOT Gate in advance of the RESET (R) Input and we get the circuit that looks like this:

| CLK | D | Q | Q’ |

| 0 | 0 | NO CHANGE | NO CHANGE |

| 0 | 1 | NO CHANGE | NO CHANGE |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

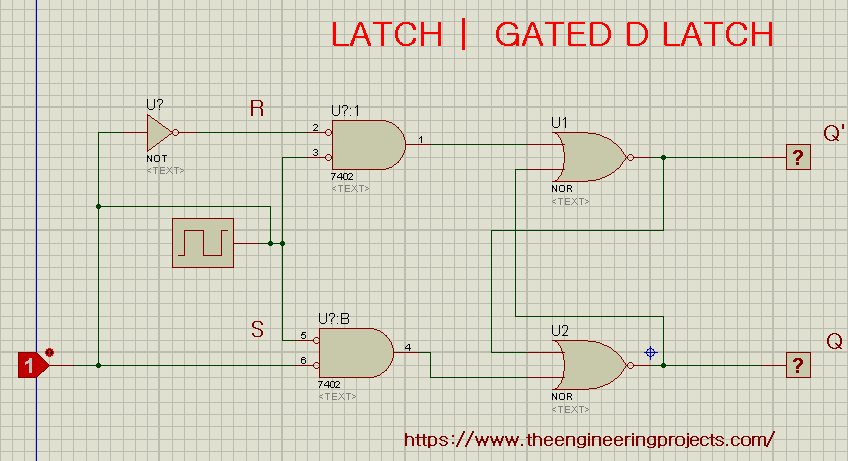

4. Gated D Latch in Proteus ISIS

This is another type of D Latch.- Connect the clock with the D input so that we alter the D input. But with this change, we see the changes in the output as well.

| CLK | D | Q | Q’ |

| 0 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |